21+ Fifo Depth Calculation

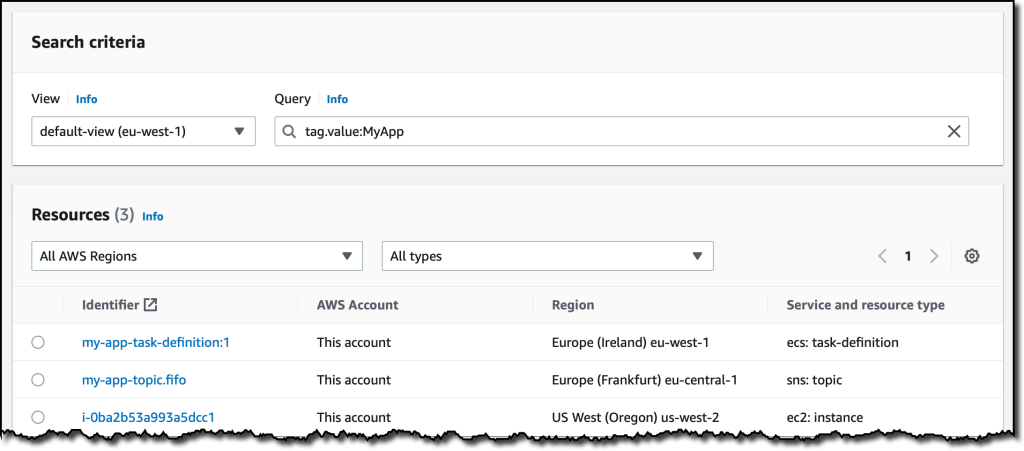

Write Clk Freq 60 MHz. FIFO Depth calculation is one of the most commonly asked Interview question.

Stm32h743vi High Performance And Dsp With Dp Fpu Arm Cortex M7 Mcu With 2mbytes Of Flash Memory 1mb Ram 480 Mhz Cpu Art Accelerator L1 Cache External Memory Interface Large Set Of Peripherals

First of all we must understand clearly the application scenarios of FIFO.

. What will be the. Consider that the Cost of Goods Sold for 250 units has to be determined using FIFO COGS Cost of Goods Sold 100times20 150times20 100 20 150 20. D B - clk_rdclk_wrB1RD Where D Depth or number of locations in FIFO to store.

Hello Everyone In this Video I have explained how to calculate FIFO Depth. This is directly related to the calculation of FIFO depth. Fifo depth calculation A FIFO has following data rate.

The write and read clock of the FIFO is running at 100 MHz and 200 MHz respectively and this write and read clock are asynchronous to each other. Input is a 16 bit parallel data at 500MHz Output is 1 bit serial data at 50 MHz I need to. Read full story at.

If you need to calculate the FIFO depth in a written test or engineering then you need to think about it yourself. Time required to read one data. The fifo parameters are as follows.

Therefore the minimum depth of FIFO is 120-37 83. FIFO Depth calculation Hi All I have a design issue I have an interface between two domains. What is depth of that.

Time required to write one data item180MHz125ns Time required to write all the data in the burst120125ns1500ns. If it is a question raised by the interviewer then if there is something unclear you should ask. Read Clk Freq 100 MHz.

Step1- FIFO Width 8 1 byte 8 bits worth of data at each buffer location Step2- Assume depth of FIFO to capture the complete buffer 100 maximum size of burst Step3- No of. Maximum Write Burst Size 1024. This page contains tidbits on writing FSM in verilog difference between blocking and non blocking assignments in verilog difference between wire and reg metastability cross frequency domain.

FIFO Depth Calculation VLSI. Incoming data 80 words at 100 clks outgoing data 8 words per 10 clks read clk write clk. FIFO Depth calculationformula Formula to calculate FIFO depth below.

May 21 2021 3 min read. Delay between writes in burst 4 clk. The write clock is slower than the read clock and there is no idle cycle during the read and write process.

Read Delay 2 clk.

Electronics Interview Questions Fifo Buffer Depth Calculation Part2 Youtube

Aws Cli Noise

Fifo Depth Calculation Vlsi Vlsi Universe

Fifo Depth Calculation How To Calculate Fifo Depth Clock Domain Crossing Cdc Vlsi Interview Youtube

Te1 Pdf Gear Electric Motor

Whole Life Insurance The Essential Guide

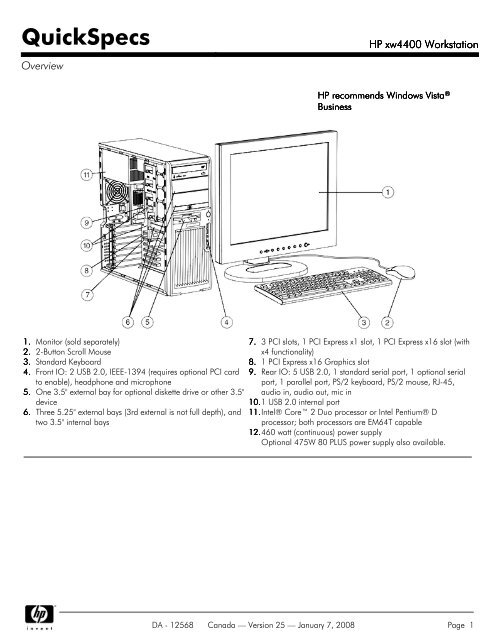

Quickspecs Ftp Directory Listing Hewlett Packard

2yjncylz9

Computer Notes Priority Queue

Fifo Depth Calculation Vlsi Read Full Story At Vlsi Universe The By Vlsi Universe Medium

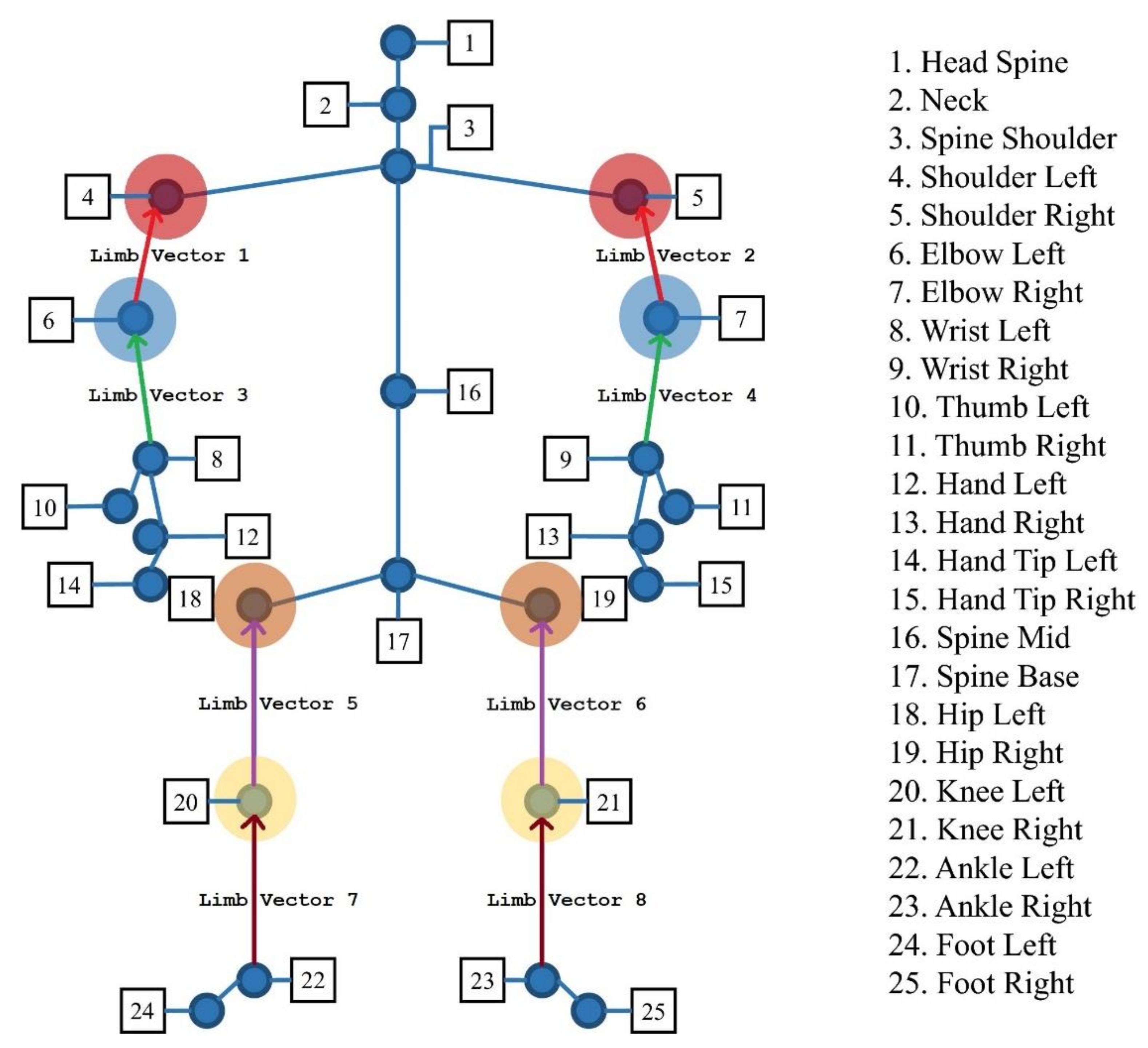

Applied Sciences Free Full Text Performance Boosting Of Scale And Rotation Invariant Human Activity Recognition Har With Lstm Networks Using Low Dimensional 3d Posture Data In Egocentric Coordinates

Transient Mediated Simulations Of Ftms Isotopic Distributions And Mass Spectra To Guide Experiment Design And Data Analysis Journal Of The American Society For Mass Spectrometry

Fifo Depth Calculation How To Calculate Fifo Depth Clock Domain Crossing Cdc Vlsi Interview Youtube

Retail Supervisor Resume Samples Velvet Jobs

Fifo Depth Calculation How To Calculate Fifo Depth Clock Domain Crossing Cdc Vlsi Interview Youtube

Tourism Impact Assessment Kimberley By Traveloscopy Editor Issuu

Fifo Depth Calculation Vlsi Vlsi Universe